SoC (सिस्टम ऑन चिप) आणि SiP (सिस्टम इन पॅकेज) हे दोन्ही आधुनिक एकात्मिक सर्किट्सच्या विकासातील महत्त्वाचे टप्पे आहेत, ज्यामुळे इलेक्ट्रॉनिक प्रणालींचे लघुकरण, कार्यक्षमता आणि एकत्रीकरण शक्य होते.

१. SoC आणि SiP च्या व्याख्या आणि मूलभूत संकल्पना

SoC (सिस्टम ऑन चिप) - संपूर्ण सिस्टम एकाच चिपमध्ये एकत्रित करणे

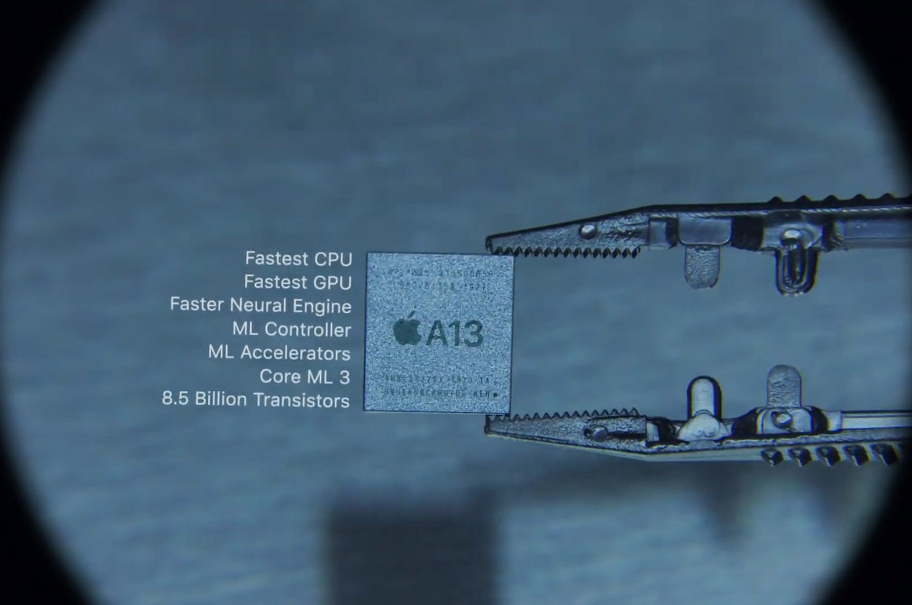

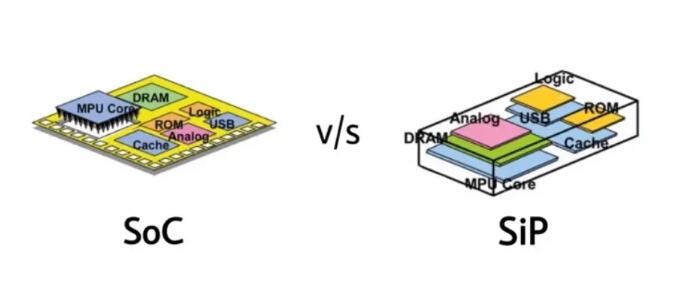

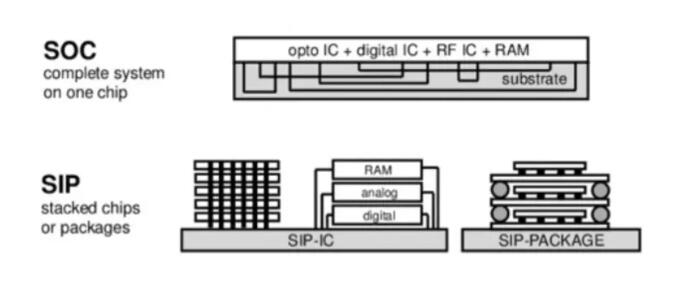

SoC हे एका गगनचुंबी इमारतीसारखे आहे, जिथे सर्व फंक्शनल मॉड्यूल्स एकाच भौतिक चिपमध्ये डिझाइन आणि एकत्रित केले जातात. SoC ची मुख्य कल्पना म्हणजे इलेक्ट्रॉनिक सिस्टमचे सर्व मुख्य घटक, ज्यामध्ये प्रोसेसर (CPU), मेमरी, कम्युनिकेशन मॉड्यूल्स, अॅनालॉग सर्किट्स, सेन्सर इंटरफेस आणि इतर विविध फंक्शनल मॉड्यूल्स समाविष्ट आहेत, एकाच चिपवर एकत्रित करणे. SoC चे फायदे त्याच्या उच्च पातळीच्या एकात्मिकरणात आणि लहान आकारात आहेत, जे कार्यप्रदर्शन, वीज वापर आणि परिमाणांमध्ये महत्त्वपूर्ण फायदे प्रदान करतात, ज्यामुळे ते उच्च-कार्यक्षमता, पॉवर-संवेदनशील उत्पादनांसाठी विशेषतः योग्य बनते. Apple स्मार्टफोनमधील प्रोसेसर ही SoC चिप्सची उदाहरणे आहेत.

उदाहरणार्थ, SoC हे शहरातील एका "सुपर बिल्डिंग" सारखे आहे, जिथे सर्व फंक्शन्स आत डिझाइन केलेले असतात आणि विविध फंक्शनल मॉड्यूल्स वेगवेगळ्या मजल्यांसारखे असतात: काही ऑफिस एरिया (प्रोसेसर), काही मनोरंजन एरिया (मेमरी) असतात आणि काही कम्युनिकेशन नेटवर्क (कम्युनिकेशन इंटरफेस) असतात, सर्व एकाच इमारतीत (चिप) केंद्रित असतात. यामुळे संपूर्ण सिस्टम एकाच सिलिकॉन चिपवर ऑपरेट करू शकते, ज्यामुळे उच्च कार्यक्षमता आणि कार्यक्षमता प्राप्त होते.

SiP (पॅकेजमधील सिस्टम) - वेगवेगळ्या चिप्स एकत्र करणे

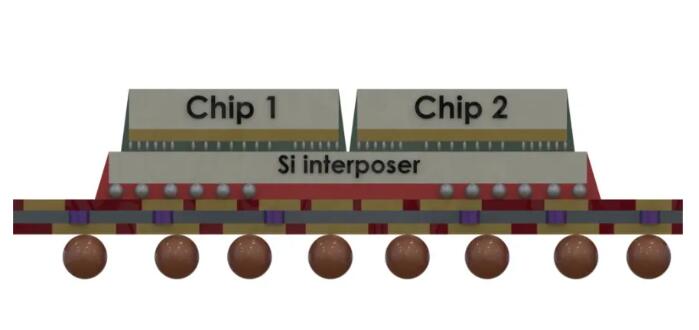

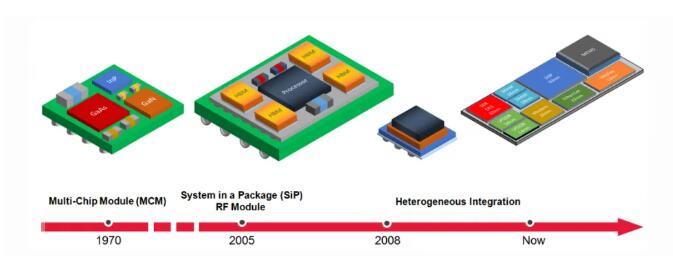

SiP तंत्रज्ञानाचा दृष्टिकोन वेगळा आहे. ते एकाच भौतिक पॅकेजमध्ये वेगवेगळ्या फंक्शन्ससह अनेक चिप्स पॅकेज करण्यासारखे आहे. ते SoC सारख्या एकाच चिपमध्ये एकत्रित करण्याऐवजी पॅकेजिंग तंत्रज्ञानाद्वारे अनेक फंक्शनल चिप्स एकत्र करण्यावर लक्ष केंद्रित करते. SiP अनेक चिप्स (प्रोसेसर, मेमरी, RF चिप्स, इ.) शेजारी शेजारी पॅकेज करण्याची किंवा एकाच मॉड्यूलमध्ये स्टॅक करण्याची परवानगी देते, ज्यामुळे सिस्टम-लेव्हल सोल्यूशन तयार होते.

SiP ची संकल्पना टूलबॉक्स असेंबल करण्यासारखी आहे. टूलबॉक्समध्ये स्क्रूड्रायव्हर्स, हॅमर आणि ड्रिल्स सारखी वेगवेगळी साधने असू शकतात. जरी ती स्वतंत्र साधने असली तरी सोयीस्कर वापरासाठी ती सर्व एकाच बॉक्समध्ये एकत्रित केली जातात. या दृष्टिकोनाचा फायदा असा आहे की प्रत्येक टूल स्वतंत्रपणे विकसित आणि तयार करता येते आणि गरजेनुसार ते सिस्टम पॅकेजमध्ये "एकत्रित" केले जाऊ शकतात, ज्यामुळे लवचिकता आणि गती मिळते.

२. तांत्रिक वैशिष्ट्ये आणि SoC आणि SiP मधील फरक

एकत्रीकरण पद्धतीतील फरक:

SoC: वेगवेगळे फंक्शनल मॉड्यूल्स (जसे की CPU, मेमरी, I/O, इ.) एकाच सिलिकॉन चिपवर थेट डिझाइन केलेले असतात. सर्व मॉड्यूल्समध्ये समान अंतर्निहित प्रक्रिया आणि डिझाइन लॉजिक असते, ज्यामुळे एक एकात्मिक प्रणाली तयार होते.

SiP: वेगवेगळ्या प्रक्रिया वापरून वेगवेगळ्या फंक्शनल चिप्स तयार केल्या जाऊ शकतात आणि नंतर 3D पॅकेजिंग तंत्रज्ञानाचा वापर करून एकाच पॅकेजिंग मॉड्यूलमध्ये एकत्र करून एक भौतिक प्रणाली तयार केली जाऊ शकते.

डिझाइनची जटिलता आणि लवचिकता:

SoC: सर्व मॉड्यूल्स एकाच चिपवर एकत्रित केलेले असल्याने, डिझाइनची जटिलता खूप जास्त आहे, विशेषतः डिजिटल, अॅनालॉग, RF आणि मेमरी सारख्या वेगवेगळ्या मॉड्यूल्सच्या सहयोगी डिझाइनसाठी. यासाठी अभियंत्यांना खोल क्रॉस-डोमेन डिझाइन क्षमता असणे आवश्यक आहे. शिवाय, SoC मधील कोणत्याही मॉड्यूलमध्ये डिझाइनची समस्या असल्यास, संपूर्ण चिप पुन्हा डिझाइन करण्याची आवश्यकता असू शकते, ज्यामुळे लक्षणीय धोके निर्माण होतात.

SiP: याउलट, SiP अधिक डिझाइन लवचिकता प्रदान करते. सिस्टममध्ये पॅकेज करण्यापूर्वी वेगवेगळे फंक्शनल मॉड्यूल डिझाइन आणि पडताळणी करता येतात. जर मॉड्यूलमध्ये समस्या उद्भवली तर फक्त ते मॉड्यूल बदलणे आवश्यक आहे, ज्यामुळे इतर भागांवर परिणाम होत नाही. यामुळे SoC च्या तुलनेत जलद विकास गती आणि कमी जोखीम देखील मिळतात.

प्रक्रिया सुसंगतता आणि आव्हाने:

SoC: डिजिटल, अॅनालॉग आणि RF सारख्या वेगवेगळ्या फंक्शन्सना एकाच चिपवर एकत्रित करणे प्रक्रियेच्या सुसंगततेमध्ये महत्त्वपूर्ण आव्हानांना तोंड देते. वेगवेगळ्या फंक्शनल मॉड्यूल्सना वेगवेगळ्या उत्पादन प्रक्रियांची आवश्यकता असते; उदाहरणार्थ, डिजिटल सर्किट्सना हाय-स्पीड, कमी-पॉवर प्रक्रियांची आवश्यकता असते, तर अॅनालॉग सर्किट्सना अधिक अचूक व्होल्टेज नियंत्रणाची आवश्यकता असू शकते. एकाच चिपवर या वेगवेगळ्या प्रक्रियांमध्ये सुसंगतता प्राप्त करणे अत्यंत कठीण आहे.

SiP: पॅकेजिंग तंत्रज्ञानाद्वारे, SiP वेगवेगळ्या प्रक्रिया वापरून उत्पादित चिप्स एकत्रित करू शकते, ज्यामुळे SoC तंत्रज्ञानासमोरील प्रक्रिया सुसंगतता समस्या सोडवता येतात. SiP एकाच पॅकेजमध्ये अनेक विषम चिप्स एकत्र काम करण्यास अनुमती देते, परंतु पॅकेजिंग तंत्रज्ञानासाठी अचूकता आवश्यकता जास्त आहेत.

संशोधन आणि विकास चक्र आणि खर्च:

SoC: SoC ला सर्व मॉड्यूल्सची सुरुवातीपासूनच रचना आणि पडताळणी आवश्यक असल्याने, डिझाइन सायकल जास्त काळ टिकते. प्रत्येक मॉड्यूलची कठोर रचना, पडताळणी आणि चाचणी करावी लागते आणि एकूण विकास प्रक्रियेला अनेक वर्षे लागू शकतात, ज्यामुळे जास्त खर्च येतो. तथापि, मोठ्या प्रमाणात उत्पादन सुरू झाल्यानंतर, उच्च एकात्मिकतेमुळे युनिटची किंमत कमी असते.

SiP: SiP साठी R&D चक्र लहान आहे. SiP पॅकेजिंगसाठी विद्यमान, सत्यापित फंक्शनल चिप्सचा थेट वापर करत असल्याने, ते मॉड्यूल रीडिझाइनसाठी लागणारा वेळ कमी करते. यामुळे उत्पादन जलद लाँच होण्यास मदत होते आणि R&D खर्च लक्षणीयरीत्या कमी होतो.

सिस्टम कामगिरी आणि आकार:

SoC: सर्व मॉड्यूल्स एकाच चिपवर असल्याने, संप्रेषण विलंब, ऊर्जा नुकसान आणि सिग्नल हस्तक्षेप कमीत कमी केला जातो, ज्यामुळे SoC ला कार्यक्षमता आणि वीज वापरात एक अतुलनीय फायदा मिळतो. त्याचा आकार कमीत कमी आहे, ज्यामुळे ते स्मार्टफोन आणि इमेज प्रोसेसिंग चिप्स सारख्या उच्च कार्यक्षमता आणि वीज आवश्यकता असलेल्या अनुप्रयोगांसाठी विशेषतः योग्य बनते.

SiP: जरी SiP ची एकत्रीकरण पातळी SoC सारखी उच्च नसली तरी, ते मल्टी-लेयर पॅकेजिंग तंत्रज्ञानाचा वापर करून वेगवेगळ्या चिप्सना कॉम्पॅक्टली पॅकेज करू शकते, ज्यामुळे पारंपारिक मल्टी-चिप सोल्यूशन्सच्या तुलनेत त्यांचा आकार लहान होतो. शिवाय, मॉड्यूल्स एकाच सिलिकॉन चिपवर एकत्रित करण्याऐवजी भौतिकरित्या पॅकेज केलेले असल्याने, कार्यक्षमता SoC शी जुळत नसली तरी, ते बहुतेक अनुप्रयोगांच्या गरजा पूर्ण करू शकते.

३. SoC आणि SiP साठी अर्ज परिस्थिती

SoC साठी अर्ज परिस्थिती:

आकार, वीज वापर आणि कामगिरीसाठी उच्च आवश्यकता असलेल्या क्षेत्रांसाठी SoC सामान्यतः योग्य आहे. उदाहरणार्थ:

स्मार्टफोन्स: स्मार्टफोन्समधील प्रोसेसर (जसे की Apple चे A-सिरीज चिप्स किंवा Qualcomm चे Snapdragon) हे सहसा अत्यंत एकात्मिक SoC असतात ज्यात CPU, GPU, AI प्रोसेसिंग युनिट्स, कम्युनिकेशन मॉड्यूल्स इत्यादींचा समावेश असतो, ज्यासाठी शक्तिशाली कामगिरी आणि कमी वीज वापर दोन्ही आवश्यक असतात.

प्रतिमा प्रक्रिया: डिजिटल कॅमेरे आणि ड्रोनमध्ये, प्रतिमा प्रक्रिया युनिट्सना अनेकदा मजबूत समांतर प्रक्रिया क्षमता आणि कमी विलंब आवश्यक असतो, जे SoC प्रभावीपणे साध्य करू शकते.

उच्च-कार्यक्षमता एम्बेडेड सिस्टीम: SoC विशेषतः कडक ऊर्जा कार्यक्षमतेच्या आवश्यकता असलेल्या लहान उपकरणांसाठी योग्य आहे, जसे की IoT उपकरणे आणि घालण्यायोग्य उपकरणे.

SiP साठी अर्ज परिस्थिती:

SiP मध्ये अनुप्रयोग परिस्थितींची विस्तृत श्रेणी आहे, जी जलद विकास आणि बहु-कार्यात्मक एकत्रीकरण आवश्यक असलेल्या क्षेत्रांसाठी योग्य आहे, जसे की:

संप्रेषण उपकरणे: बेस स्टेशन, राउटर इत्यादींसाठी, SiP अनेक RF आणि डिजिटल सिग्नल प्रोसेसर एकत्रित करू शकते, ज्यामुळे उत्पादन विकास चक्र वेगवान होते.

ग्राहक इलेक्ट्रॉनिक्स: स्मार्टवॉच आणि ब्लूटूथ हेडसेट सारख्या उत्पादनांसाठी, ज्यांचे अपग्रेड सायकल जलद असते, SiP तंत्रज्ञान नवीन वैशिष्ट्यपूर्ण उत्पादनांचे जलद लाँचिंग करण्यास अनुमती देते.

ऑटोमोटिव्ह इलेक्ट्रॉनिक्स: ऑटोमोटिव्ह सिस्टीममधील कंट्रोल मॉड्यूल्स आणि रडार सिस्टीम वेगवेगळ्या फंक्शनल मॉड्यूल्सना जलद एकत्रित करण्यासाठी SiP तंत्रज्ञानाचा वापर करू शकतात.

४. SoC आणि SiP चे भविष्यातील विकास ट्रेंड

SoC विकासातील ट्रेंड:

SoC उच्च एकात्मता आणि विषम एकात्मतेकडे विकसित होत राहील, ज्यामध्ये AI प्रोसेसर, 5G कम्युनिकेशन मॉड्यूल्स आणि इतर फंक्शन्सचे अधिक एकात्मता समाविष्ट असेल, ज्यामुळे बुद्धिमान उपकरणांचा पुढील विकास होईल.

SiP विकासातील ट्रेंड:

वेगाने बदलणाऱ्या बाजारातील मागण्या पूर्ण करण्यासाठी वेगवेगळ्या प्रक्रिया आणि कार्यांसह चिप्सचे घट्ट पॅकेजिंग करण्यासाठी SiP 2.5D आणि 3D पॅकेजिंग प्रगतीसारख्या प्रगत पॅकेजिंग तंत्रज्ञानावर अधिकाधिक अवलंबून राहील.

५. निष्कर्ष

SoC हे एका बहु-कार्यक्षम सुपर स्कायस्केपर इमारतीसारखे आहे, ज्यामध्ये सर्व फंक्शनल मॉड्यूल्स एकाच डिझाइनमध्ये केंद्रित केले जातात, जे कामगिरी, आकार आणि वीज वापरासाठी अत्यंत उच्च आवश्यकता असलेल्या अनुप्रयोगांसाठी योग्य आहेत. दुसरीकडे, SiP हे वेगवेगळ्या फंक्शनल चिप्सना एका सिस्टममध्ये "पॅकेजिंग" करण्यासारखे आहे, लवचिकता आणि जलद विकासावर अधिक लक्ष केंद्रित करते, विशेषतः जलद अद्यतनांची आवश्यकता असलेल्या ग्राहक इलेक्ट्रॉनिक्ससाठी योग्य. दोन्हीमध्ये त्यांची ताकद आहे: SoC इष्टतम सिस्टम कामगिरी आणि आकार ऑप्टिमायझेशनवर भर देते, तर SiP सिस्टम लवचिकता आणि विकास चक्राच्या ऑप्टिमायझेशनवर भर देते.

पोस्ट वेळ: ऑक्टोबर-२८-२०२४